Over the last 50 years, advances in silicon lithography have driven the exponential miniaturization of electronics, underpinning Moore’s Law. This techno-economic model has enabled the technology industry to double the performance and functionality of digital electronics every two years while maintaining fixed costs, power, and area. However, as transistors approach atomic limits and fabrication costs rise, Moore’s Law is beginning to falter.

At Berkeley Lab, our researchers are reimagining the future of computing beyond Moore’s Law and anticipating the challenges ahead. We are exploring a range of novel opportunities and strategies to continue improving computing performance, functionality, and efficiency. These include superconducting electronics, post-CMOS transistors, new physical phenomena such as skyrmions, and innovative models of computation. Additionally, we are investigating new technologies and computing systems that surpass the performance limitations caused by the tapering of lithographic scaling, including heterogeneous accelerators, neuromorphic computing, and quantum computing. The introduction of quantum devices demands even more aggressive advancements in algorithms and software, in addition to classical hardware for control and use in hybrid algorithms.

Our researchers provide modeling capabilities for new materials, hardware design, and evaluation, as well as algorithms and software developments to enhance performance, energy efficiency, integration, and scaling. Our work in algorithms and software enables emerging scientific challenges, informs hardware designers of computational requirements and options, and adapts to future hardware features.

Our Research Pillars:

- Heterogeneous Architectures

- Neuromorphic Computing

- Quantum Computing

- Post-Moore Microelectronics

- Superconducting Electronics

PARADISE++

PARADISE++ is a simulation environment that helps researchers design and test new computer systems—before they’re built. By modeling the performance and energy use of future supercomputers, PARADISE++ guides smarter investments in advanced technology and accelerates breakthroughs in science, engineering, and industry.

GASNet

GASNet is a communications library that helps scientists run large-scale simulations efficiently on the world’s fastest supercomputers. By enabling high-performance data exchange, GASNet supports breakthroughs across science, engineering, and industry.

UPC++

UPC++ is a programming library that makes it easier for researchers to write software that runs efficiently on modern, large-scale supercomputers. By improving performance and scalability, UPC++ helps scientists tackle complex problems in fields ranging from energy to healthcare.

SuperLU

SuperLU is a mathematical software library that solves the large systems of equations at the heart of many scientific simulations. By delivering fast and reliable results, SuperLU empowers researchers to advance discovery in areas such as engineering, materials science, and physics.

STRUMPACK

STRUMPACK is a software package that efficiently solves large, structured systems of equations, which are common in advanced modeling and simulation. By speeding up complex calculations, STRUMPACK enables researchers to address challenges in science and engineering more effectively.

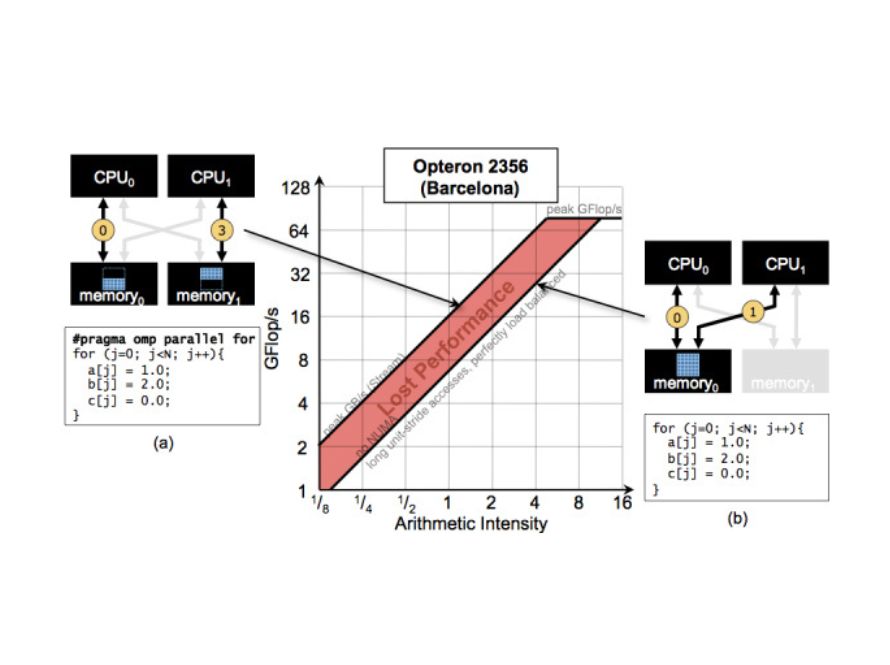

Roofline Performance Model

The Roofline Performance Model is a user-friendly tool that helps scientists and engineers maximize the performance of their computer codes. By quickly identifying bottlenecks, it ensures that researchers get the most out of today’s powerful computing systems.

Superconducting Race Logic Accelerators

Superconducting Race Logic Accelerators are pioneering a new kind of ultra-fast, energy-efficient computer hardware. By exploring alternatives to traditional chips, this project is opening new possibilities for scientific computing and artificial intelligence.

Chiplet Technology & Open Compute Project Collaboration

AMCR collaborates with industry partners to advance modular chiplet technology and open hardware standards. These efforts reduce costs, speed up innovation, and help ensure U.S. leadership in designing the computers of the future.

HamPerf

HamPerf is a quantum benchmarking approach that evaluates the computational utility of quantum processors by focusing on the underlying mathematical descriptions (Hamiltonians) of problems, enabling fair comparisons across different hardware and algorithms.

INDIE

INDIE (Intelligent Distribution for Advanced Wireless Networks with Scientific Data Microservices) is a software platform that provides intelligent data management, computational task composition, and workflow coordination for scientific applications across advanced wireless networks like 5G and 6G.

Cryogenic Control for Quantum

Cryogenic Control for Quantum explores innovative low-temperature control solutions using superconducting technology to enable scalable, high-fidelity control of quantum systems, overcoming the limitations of current room-temperature and cryo-CMOS approaches.

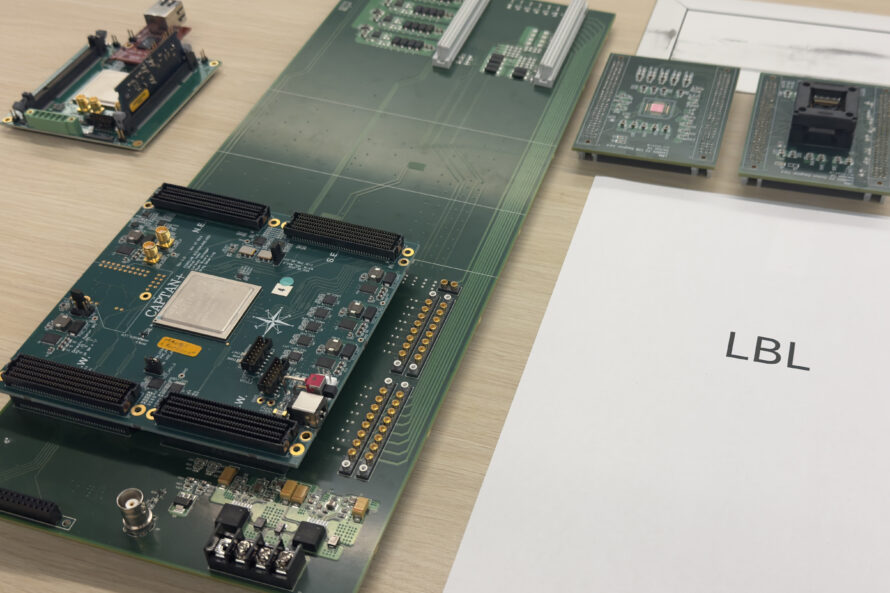

VIAS

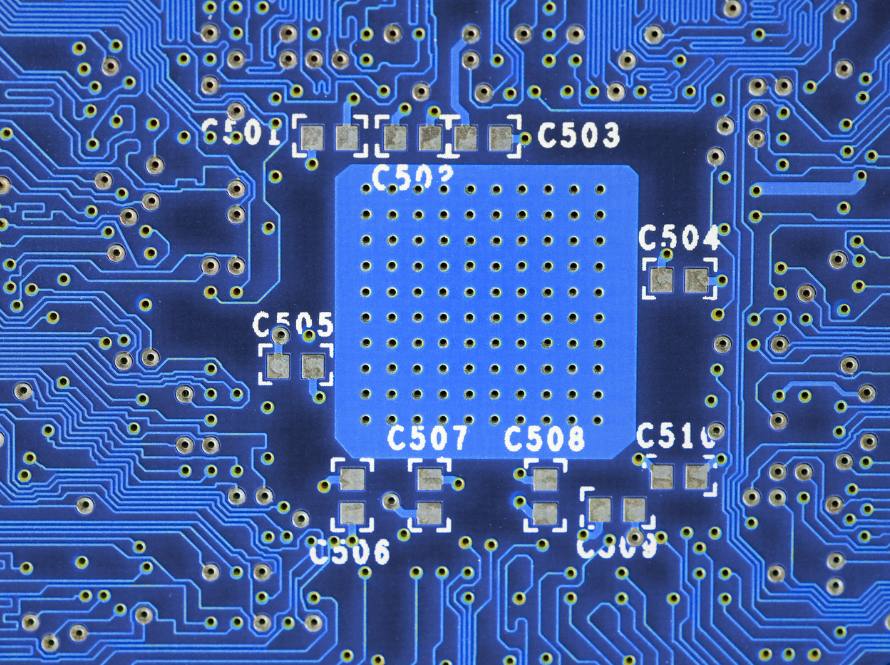

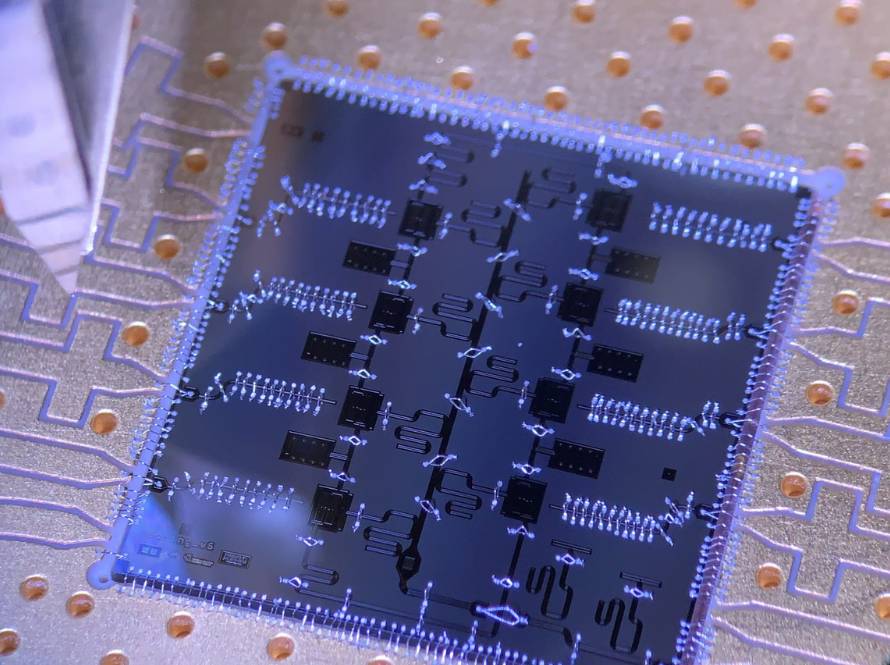

The Vertically Integrated Artificial Intelligence for Sensing and High-Performance Computing (VIAS) project develops next-generation detectors that use vertically integrated, chiplet-based circuits and advanced AI hardware to enable fast, efficient data analysis in challenging environments.

ENDURABLE

ENDURABLE is a toolkit that streamlines the building and optimization of complex artificial intelligence (AI) models. By making it easier to collect and manage data, ENDURABLE accelerates discovery in medicine, energy, and environmental research.

FlexBrain

FlexBrain is a neuromorphic computing framework that combines spiking and analog neural network dynamics to enable energy-efficient, flexible, and context-dependent processing for edge applications such as real-time brain activity decoding and high-throughput scientific data analysis.

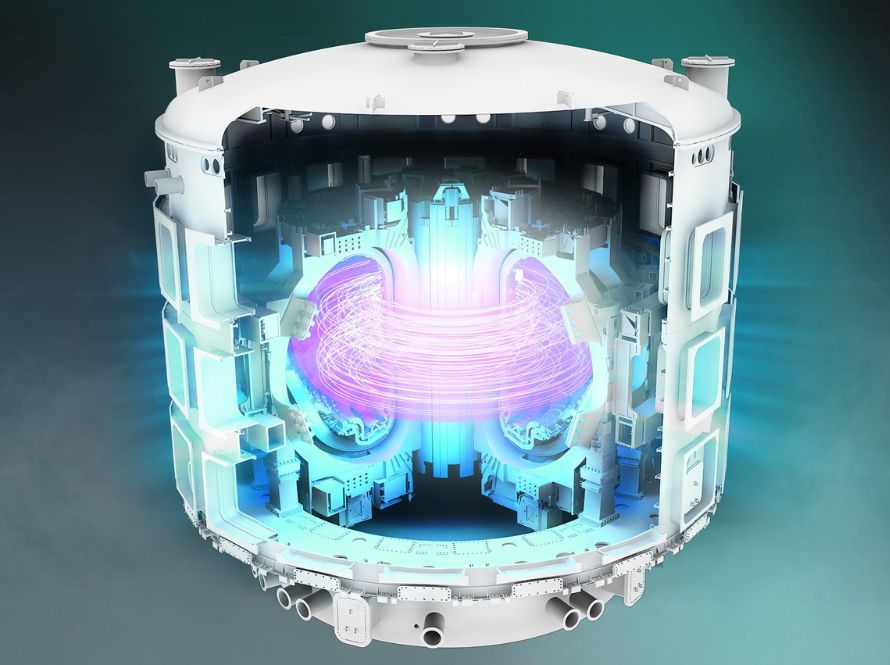

Cryo-Phoenix

Cryo-Phoenix is a project to develop and evaluate a superconducting electronics-based supercomputing system architecture—leveraging specialized accelerators, high-density wafer stacking, and ultra-high bandwidth photonic interconnects—to achieve Zetta-scale performance with dramatically improved energy efficiency, addressing key DOE goals for next-generation supercomputing.

Computer Architecture Group

Quantum Information Science and Technology Research

Microelectronic Research